莎克妊容刻抬裙完仆篡蛊沏捍

第一章 单元测试

1、

相对于数字电路来说,模拟集成电路的设计更加基础,更加灵活。

A:对

B:错

答案: 对

2、

MOSFET的特征尺寸越来越小,本征速度越来越快(已可与双极器件相比较),现在几GHz~几十GHz的CMOS模拟集成电路已经可批量生产。

A:对

B:错

答案: 对

3、

CMOS电路已成为当今SOC设计的主流制造技术。

A:对

B:错

答案: 对

4、

模拟设计涉及到在速度、功耗、增益、精度、电源电压等多种因素间进行折衷

A:对

B:错

答案: 对

5、

模拟电路许多效应的建模和仿真仍然存在问题,模拟设计需要设计者利用经验和直觉来分析仿真结果

A:对

B:错

答案: 对

6、

跟数字集成电路设计一样,目前高性能模拟集成电路的设计已经能自动完成。

A:对

B:错

答案: 错

第二章 单元测试

1、

MOS器件的源端和漏端不可以共用,不可以互换。

A:对

B:错

答案: 错

2、

下列关于MOS版图说法不正确的是()

A:栅接触孔为什么开在沟道区外

B:版图中沟道长度L的最小值由工艺决定

C:源结和漏结的一个尺寸等于W,另外一个尺寸要满足接触孔的需要,并且要满足设计规则

D:版图中栅极的接触孔可以开在沟道区

答案: 版图中栅极的接触孔可以开在沟道区

3、

下列说法正确的是()

A:MOSFET是四端器件

B:MOS管正常工作的基本条件是: 所有衬源(B、S)、衬漏(B、D)PN结必须反偏(或者零偏)!

C:阱中MOSFET衬底常接源极S

D:N阱接最低电位

答案: N阱接最低电位

4、

下列关于阈值电压的说法,不正确的是()

A:NFET的阈值电压定义为当界面的电子浓度等于p型衬底的多子浓度时的栅压VGS

B:在器件制造过程中,可通过向沟道区注入杂质来调整阈值电压

C:当VGS>VTH时,NMOS器件导通

D:若VTH=0,则 NMOS器件关断

答案: 若VTH=0,则 NMOS器件关断

5、

下列说法正确的是()

A:VGS<VTH时,NMOS器件工作在截止区

B:VGS ≥VTH,VDS≤ VGS – VTH时,NMOS器件工作在线性区

C:VGS ≥ VTH,VDS ≥ VGS – VTH时,NMOS器件工作在饱和区

D:VGS<=0时,NMOS器件不工作

答案: VGS<VTH时,NMOS器件工作在截止区;VGS ≥VTH,VDS≤ VGS – VTH时,NMOS器件工作在线性区;VGS ≥ VTH,VDS ≥ VGS – VTH时,NMOS器件工作在饱和区

6、

下列对器件尺寸参数描述正确的有()

A:L是器件的沟道长度,W是器件的宽度

B:tox是器件栅氧化层的厚度,由工艺决定

C:一般所说的90nm工艺,其中的90nm是指器件的最小沟道长度L

D:一般所说的90nm工艺,其中的90nm是指器件的栅氧化层的厚度tox

答案: L是器件的沟道长度,W是器件的宽度;tox是器件栅氧化层的厚度,由工艺决定;一般所说的90nm工艺,其中的90nm是指器件的最小沟道长度L

7、

如果一个电路的最高电压是VDD,最低电压是VSS,那么NMOS器件的衬底应该接VDD。

A:对

B:错

答案: 错

8、

一般MOS器件的源漏是对称的,这告诉我们要根据实际集成电路的情况来判断电路的源极和漏极。

A:对

B:错

答案: 对

9、

下列关于体效应的说法,正确的是()

A:改变衬底电势Vsub可能会产生体效应。

B:不改变衬底电势Vsub也可能会产生体效应。

C:源电压相对于Vsub发生改变,使得源衬电势差VSB不为0,就会产生体效应。

D:体效应导致设计参数复杂,模拟集成电路设计往往不希望其存在,但也有利用体效应的电路。

答案: 改变衬底电势Vsub可能会产生体效应。;不改变衬底电势Vsub也可能会产生体效应。;源电压相对于Vsub发生改变,使得源衬电势差VSB不为0,就会产生体效应。;体效应导致设计参数复杂,模拟集成电路设计往往不希望其存在,但也有利用体效应的电路。

10、

下列关于沟道长度调制效应说法正确的是()

A:器件的导电沟道越长,沟道调制效应系数越小。

B:器件的沟道调制效应系数由工艺决定。

C:器件的导电沟道越短,沟道调制效应系数越小。

D:沟道调制效应说明饱和区器件的电流会受到漏源电压的影响。

答案: 器件的导电沟道越长,沟道调制效应系数越小。;器件的沟道调制效应系数由工艺决定。;沟道调制效应说明饱和区器件的电流会受到漏源电压的影响。

11、

下列关于亚阈值导电特性的说法正确的是()

A:亚阈值区的跨导比饱和区(强反型区)跨导大,有利于实现大的放大倍数

B:MOS管亚阈值电流ID一般为几十~几百nA, 常用于低功耗放大器、带隙基准设计

C:MOS管VGS由0增大到大于阈值电压VTH,经历截止—弱反型—强反型,这是一个渐进的过程,故当VGS<VTH时,仍有IDS存在

D:当VGS<VTH时,漏极电流ID以有限速度下降,导致功率损耗或模拟信息的丢失

答案: 亚阈值区的跨导比饱和区(强反型区)跨导大,有利于实现大的放大倍数;MOS管亚阈值电流ID一般为几十~几百nA, 常用于低功耗放大器、带隙基准设计;MOS管VGS由0增大到大于阈值电压VTH,经历截止—弱反型—强反型,这是一个渐进的过程,故当VGS<VTH时,仍有IDS存在;当VGS<VTH时,漏极电流ID以有限速度下降,导致功率损耗或模拟信息的丢失

12、

下列关于MOS模型的说法正确的有()

A:MOS器件的大信号模型一般由I/V特性关系式,各寄生电容计算式等推导建立

B:当信号相对直流偏置工作点而言较小且不会显著影响直流工作点时,可用小信号模型简化计算

C:MOS器件的低频小信号模型,主要考虑了跨导,体效应以及沟道调制效应等参数

D:MOS器件的高频小信号模型,除考虑跨导,体效应以及沟道调制效应等参数,还需要考虑各个寄生电容和寄生电阻的影响

答案: MOS器件的大信号模型一般由I/V特性关系式,各寄生电容计算式等推导建立;当信号相对直流偏置工作点而言较小且不会显著影响直流工作点时,可用小信号模型简化计算;MOS器件的低频小信号模型,主要考虑了跨导,体效应以及沟道调制效应等参数;MOS器件的高频小信号模型,除考虑跨导,体效应以及沟道调制效应等参数,还需要考虑各个寄生电容和寄生电阻的影响

13、

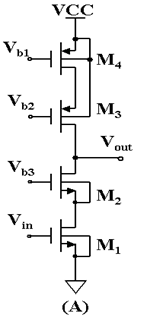

判断制造下列电路的衬底类型

A:N型衬底

B:P型衬底

答案: N型衬底

14、

判断器件为NMOS器件还是PMOS器件?

A:NMOS

B:PMOS

C:什么都不是

答案: PMOS

第三章 单元测试

1、

下列关于放大的说法,正确的是()

A:在大多数模拟电路和许多数字电路中,放大是一个基本功能。

B:我们放大一个模拟或数字信号是因为这个信号太小而不能驱动负载,或者不能克服后继的噪声

C:放大不能为数字电路提供逻辑电平。

D:放大在反馈系统中起着重要作用。

答案: 在大多数模拟电路和许多数字电路中,放大是一个基本功能。;我们放大一个模拟或数字信号是因为这个信号太小而不能驱动负载,或者不能克服后继的噪声;放大在反馈系统中起着重要作用。

2、

下列关于小信号的说法,正确的是()

A:小信号使电路偏置点受到的扰动可忽略不记

B:若小信号变化幅度过大,则会影响直流偏置点,需用大信号分析

C:假定某MOS器件的栅源过驱动电压VGS – VTH = 0.5V,则|vgs(t)|可视为小信号的变化范围为10mV

D:一般小信号是交流信号

答案: 小信号使电路偏置点受到的扰动可忽略不记;若小信号变化幅度过大,则会影响直流偏置点,需用大信号分析;一般小信号是交流信号

3、

以电阻RD为负载的共源级电路的小信号增益的表达式有()

A:

B:

C:

D:

答案: ;;;

4、

对于以电阻RD为负载的共源级电路,增大其小信号增益的措施有()

A:增大器件M1的宽长比W/L

B:减小器件M1的宽长比W/L

C:增大电阻RD上的电压VRD

D:减小漏极电流ID

答案: 增大器件M1的宽长比W/L;增大电阻RD上的电压VRD;减小漏极电流ID

5、

对于以电阻RD为负载的共源级电路,增大器件的宽长比W/L,可以增大电路的小信号增益AV ,但MOS管寄生电容相应增加,电路的高频响应会变差,其3dB转折频率点会下降

A:对

B:错

答案: 对

6、

对于以电阻RD为负载的共源级电路,增大电阻上的电压VRD, 可以增大电路的小信号增益AV ,但VDS 会下降,从而导致放大器静态工作点下移,输出电压的摆幅会减小

A:对

B:错

答案: 对

7、

对于以电阻RD为负载的共源级电路,减小ID, 可以增大电路的小信号增益AV

A:对

B:错

答案: 对

8、

对于以电阻RD为负载的共源级电路,增大电阻RD,可以增大电路的小信号增益AV,但会导致电路的版图面积增加,电阻噪声增大,放大器速度下降。

A:对

B:错

答案: 对

9、

图中的M1被偏置在饱和区,则电路的小信号电压增益,说明使用电流源作负载可提高增益。

A:对

B:错

答案: 对

10、

下列说法正确的是()

A:所谓二极管连接的MOS管实际上是将MOS器件的栅极和源极短接,起到小信号电阻的作用

B:MOS管二极管连接并导通时,不论是NMOS还是PMOS管, 均工作在饱和区

C:二极管连接的PMOS管作负载的共源极电路的小信号增益只与W/L有关,与偏置电流无关,即输入与输出呈线性

D:二极管连接的PMOS管作负载的共源极电路的小信号增益是两管过驱动电压之比,AV越大,Vov2越大,Voutmax越小

答案: MOS管二极管连接并导通时,不论是NMOS还是PMOS管, 均工作在饱和区;二极管连接的PMOS管作负载的共源极电路的小信号增益只与W/L有关,与偏置电流无关,即输入与输出呈线性;二极管连接的PMOS管作负载的共源极电路的小信号增益是两管过驱动电压之比,AV越大,Vov2越大,Voutmax越小

11、

下列关于源极跟随器的说法正确的有()

A:源极跟随器的AV≤1

B:源极跟随器一般只用来驱动小电容(或高阻)负载,不宜用来驱动低阻、大电容负载

C:源极跟随器可用来构成电平位移电路

D:相对于共源级电路来说,源极跟随器增益很大,输出阻抗很高。

答案: 源极跟随器的AV≤1;源极跟随器一般只用来驱动小电容(或高阻)负载,不宜用来驱动低阻、大电容负载;源极跟随器可用来构成电平位移电路

12、

下列关于共栅放大器的说法正确的有()

A:输入阻抗与RD有关,有阻抗变换特性

B:输出阻抗高,可用于提高增益和构成高性能恒流源

C:其增益与共源级放大电路增益相同

D:常同CS联合构成CS—CG放大器,用于高速运放的差分输入放大级

答案: 输入阻抗与RD有关,有阻抗变换特性;输出阻抗高,可用于提高增益和构成高性能恒流源;常同CS联合构成CS—CG放大器,用于高速运放的差分输入放大级

13、

如图(a) (b) (c)三个电路,若电路中ID相等,输出阻抗最大的是()

A:(a)

B:(b)

C:(c)

D:三个电路都是

答案: (c)

14、

关于共源共栅电路下列说法正确的有()

A:共源共栅结构具有高输出阻抗特性

B:共源共栅电流源可近似代替理想恒流源

C:共源共栅结构具有高输出摆幅

D:共源共栅结构具有屏蔽特性

答案: 共源共栅结构具有高输出阻抗特性;共源共栅电流源可近似代替理想恒流源;共源共栅结构具有屏蔽特性

15、

如图(a) (b) (c)三个电路,若电路中ID相等,对增益讨论正确的是()

A:(c)增益最大

B:(b)增益为(a)的两倍

C:(b)增益最大

D:(a)增益最小

答案: (c)增益最大;(b)增益为(a)的两倍;(a)增益最小

上方为免费预览版答案,如需购买完整答案,请点击下方红字

点关注,不迷路,微信扫一扫下方二维码

关注我们的公众号:阿布查查 随时查看答案,网课轻松过

为了方便下次阅读,建议在浏览器添加书签收藏本网页

电脑浏览器添加/查看书签方法

1.按键盘的ctrl键+D键,收藏本页面

2.下次如何查看收藏的网页?

点击浏览器右上角-【工具】或者【收藏夹】查看收藏的网页

手机浏览器添加/查看书签方法

一、百度APP添加/查看书签方法

1.点击底部五角星收藏本网页

2.下次如何查看收藏的网页?

点击右上角【┇】-再点击【收藏中心】查看

二、其他手机浏览器添加/查看书签方法

1.点击【设置】-【添加书签】收藏本网页

2.下次如何查看收藏的网页?

点击【设置】-【书签/历史】查看收藏的网页

缆趁句败群辽纺仆患啃膜功猫